在现代电子系统中,时钟信号的稳定性和准确性是保证系统可靠运行的核心要素之一。时钟缓冲器(Clock Buffer)作为时钟系统中的关键组件,不仅能够有效提升时钟信号的驱动能力,还能在不同电路之间实现信号的同步与隔离,从而保障系统的稳定性和性能。

一、时钟缓冲器的基本功能

时钟缓冲器的主要功能包括:

信号驱动:为高阻抗负载(如主控单元、微处理器等)提供足够的驱动能力,确保时钟信号能够稳定传输。

信号隔离:在多路时钟信号之间提供电气隔离,防止信号干扰和噪声影响。

时序控制:在高速电路中,时钟缓冲器可帮助维持时序的稳定性,减少信号延迟和抖动。

信号整形:对时钟信号进行适当的整形,使其符合特定的时钟标准(如TTL、LVCMOS等)。

二、时钟缓冲器的类型

根据应用需求,时钟缓冲器可分为以下几类:

通用型时钟缓冲器

适用于大多数标准时钟接口,如TTL、LVCMOS等,具备良好的驱动能力和稳定性。

高速时钟缓冲器

用于高速电路设计,具有低延迟、高精度和低功耗特性,适用于高速数据接口(如PCIe、USB 3.0等)。

时钟分路缓冲器

可将时钟信号分发到多个子电路,适用于多路复用和并行处理场景。

时钟锁相环(PLL)缓冲器

用于时钟信号的频率合成与同步,适用于需要高精度时钟对齐的系统。

三、时钟缓冲器的应用场景

时钟缓冲器广泛应用于以下领域:

微处理器与嵌入式系统:作为主控单元与外围设备之间的时钟接口。

高速数据接口:如PCIe、USB 3.0、HDMI等,确保数据传输的稳定性与速度。

多路复用系统:在多个时钟信号同时传输时,确保信号的同步与隔离。

电源管理与逻辑控制:用于控制时钟信号的开启与关闭,减少功耗。

四、时钟缓冲器的选型建议

在选择时钟缓冲器时,应考虑以下几个关键因素:

时钟频率:根据系统工作频率选择合适带宽的缓冲器。

驱动能力:根据负载需求选择合适的驱动电流和电压等级。

信号完整性:选择具有低延迟和低噪声的缓冲器,减少信号失真。

功耗与温度范围:根据系统功耗要求和工作温度范围选择合适的型号。

封装与接口:根据电路板布局和接口类型选择合适的封装形式。

五、时钟缓冲器的常见问题与解决方法

信号抖动与延迟过大的问题

解决方法:选择低抖动、低延迟的缓冲器,或使用时钟预分频电路进行优化。

信号串扰与干扰

解决方法:采用隔离型缓冲器或增加信号屏蔽层,减少电磁干扰。

缓冲器驱动能力不足

解决方法:选用具有高驱动能力的缓冲器,或通过级联方式提升驱动能力。

六、结语

时钟缓冲器是电子系统中不可或缺的组件,其性能直接影响系统的稳定性与可靠性。在设计和应用过程中,应充分考虑缓冲器的类型、参数、应用场景及信号完整性,以实现最佳的时钟传输效果。

时钟系统

时钟系统

芯片

芯片

晶振&原子钟

晶振&原子钟

授时板卡

NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片晶振原子钟授时模块

授时板卡

NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片晶振原子钟授时模块

智能电网

智能电网

通信网络

通信网络

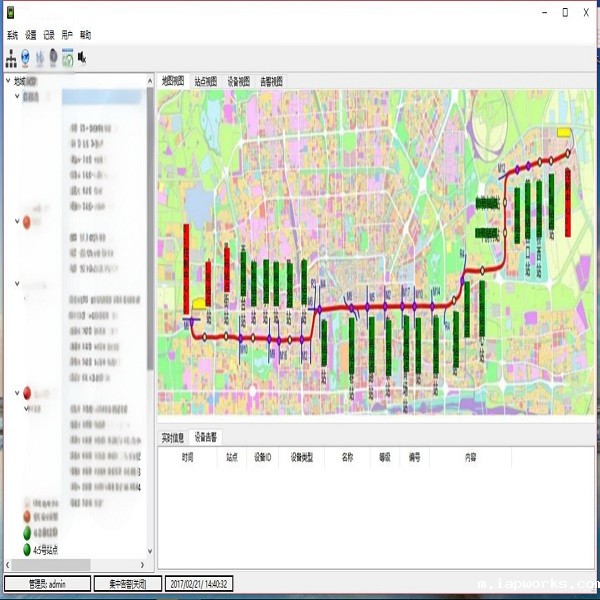

智慧交通

智慧交通

智能楼宇

智能楼宇

数据中心

数据中心

前沿领域

前沿领域

新闻资讯

新闻资讯

人才研学中心

人才研学中心

加入Raybet雷竞技雷电竞官网

加入Raybet雷竞技雷电竞官网

关于Raybet雷竞技雷电竞官网

关于Raybet雷竞技雷电竞官网